模擬集成電路設(shè)計精粹 第三章 集成電路設(shè)計基礎(chǔ)

集成電路設(shè)計是現(xiàn)代電子工程的核心領(lǐng)域之一,尤其模擬集成電路設(shè)計,因其涉及連續(xù)信號的精確處理,對設(shè)計者的理論功底和實踐經(jīng)驗提出了更高要求。本章將系統(tǒng)性地探討模擬集成電路設(shè)計的基礎(chǔ)概念、關(guān)鍵技術(shù)與設(shè)計流程。

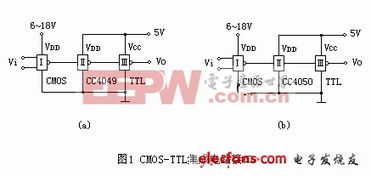

模擬集成電路設(shè)計的核心目標(biāo)是在給定的工藝約束下,實現(xiàn)特定的電氣性能指標(biāo),如增益、帶寬、噪聲、功耗和線性度等。與數(shù)字電路不同,模擬電路對工藝偏差、溫度變化和電源波動更為敏感,因此設(shè)計的魯棒性至關(guān)重要。設(shè)計師必須深入理解器件物理特性,特別是MOSFET在亞微米及以下節(jié)點的行為,包括短溝道效應(yīng)、漏致勢壘降低(DIBL)和遷移率退化等現(xiàn)象。

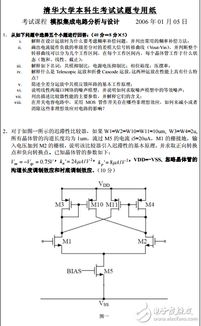

設(shè)計流程通常始于系統(tǒng)級規(guī)劃,明確電路的功能模塊劃分和性能預(yù)算分配。隨后進入電路級設(shè)計,這是本章的重點。在這一階段,設(shè)計師需要選擇合適的電路拓?fù)浣Y(jié)構(gòu),例如差分對、電流鏡、共源共柵結(jié)構(gòu)等,并進行初步的手工計算以確定器件尺寸和偏置條件。小信號模型分析是必不可少的工具,用于評估增益、頻率響應(yīng)和穩(wěn)定性。大信號分析也不可忽視,它關(guān)乎電路的動態(tài)范圍和失真特性。

仿真驗證是設(shè)計流程中的關(guān)鍵環(huán)節(jié)。利用EDA工具進行直流、交流和瞬態(tài)仿真,可以驗證設(shè)計是否滿足指標(biāo),并識別潛在問題,如失調(diào)電壓、寄生振蕩或熱效應(yīng)。蒙特卡洛分析幫助評估工藝變異下的電路性能分布,從而指導(dǎo)設(shè)計優(yōu)化以提高良率。

版圖設(shè)計是物理實現(xiàn)的橋梁,其質(zhì)量直接影響電路性能。模擬版圖需特別關(guān)注匹配性、對稱性和寄生效應(yīng)控制。例如,差分對通常采用共質(zhì)心結(jié)構(gòu)以降低工藝梯度影響,而敏感節(jié)點則應(yīng)避免長走線以減少寄生電容和電阻。電源和地線的規(guī)劃、襯底噪聲隔離以及ESD保護電路的設(shè)計都是版圖階段必須謹(jǐn)慎處理的問題。

測試與驗證是設(shè)計的收官之筆。通過測試芯片的量測數(shù)據(jù),設(shè)計師可以對比仿真結(jié)果,分析差異并積累經(jīng)驗,從而形成設(shè)計迭代的閉環(huán)。本章強調(diào),成功的模擬集成電路設(shè)計是理論、工具和經(jīng)驗的三者結(jié)合,需要設(shè)計師在嚴(yán)謹(jǐn)?shù)墓こ虒嵺`中不斷深化對電路本質(zhì)的理解。

第三章為讀者奠定了集成電路設(shè)計的堅實基礎(chǔ),從概念到實現(xiàn),逐步揭示了模擬電路設(shè)計的精髓所在,為后續(xù)更深入的專業(yè)學(xué)習(xí)鋪平道路。

如若轉(zhuǎn)載,請注明出處:http://m.aywcug.cn/product/74.html

更新時間:2026-04-14 06:03:36